Approximate Computing for Smart Edge Processing

1.9.2017 – 31.8.2021

590 000 euros

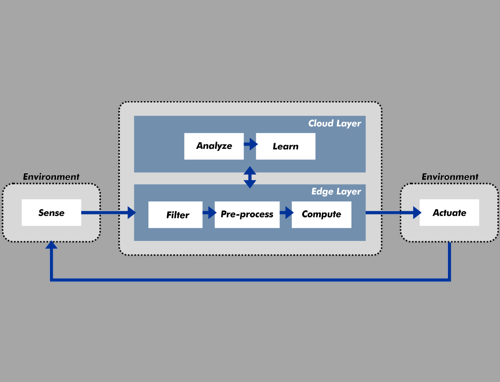

Emerging application domains such as artificial intelligence, virtual and augmented reality, cyber-physical systems and Internet-of-things (IoT) etc., provide intelligence to machines and the environment in which they function by integrating sensing, computation and actuation capabilities. To make intelligent decisions and influence the environment meaningfully, these applications require high performance in real-time, beyond the scope of traditional computing applications. Ambient intelligence application domains, in particular in the context of Internet-of-Things, require high performance in real-time within lower energy budgets. Power challenges have limited the performance and energy gains of existing mobile processing platforms. Approximate Computing has emerged as an alternative that leverages inherent error resilience in computing applications to trade-off accuracy for performance and energy gains. We address the performance and energy issues of emerging applications and power challenges of existing hardware platforms simultaneously through approximate computing. The objective of this proposal is to implement hardware and software techniques to design an ecosystem that supports approximation. We orchestrate approximation in two steps, software layer – to identify and annotate approximable regions of applications, hardware layer- to exploit error resilient tasks by executing them on inaccurate hardware. We design modular reconfigurable processor cores, butterfly cores, that can switch their mode of execution from accurate to approximate on demand, based on application requirements and system dynamics. We integrate butterfly cores into a chip multi-processor, the butterfly processor, for high performance and flexibility in choice of quality of service. We bridge the gap among different layers of computing stack in realizing approximate hardware through architectural design and implementation of a general purpose approximate hardware. To support the run-time reconfiguration of processor mode (accurate and approximate), we implement hierarchical system management to optimize power, energy, performance and accuracy at the same time.